#### ES

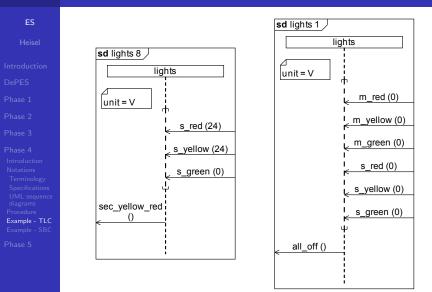

Heisel

Introductio

DePES

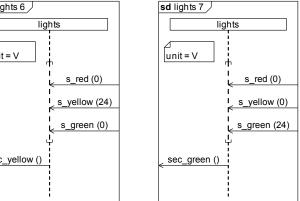

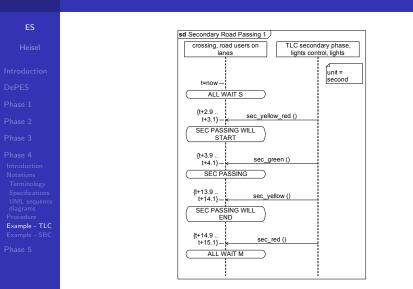

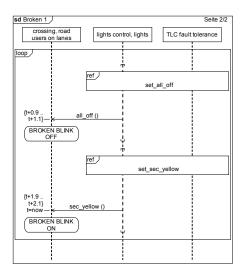

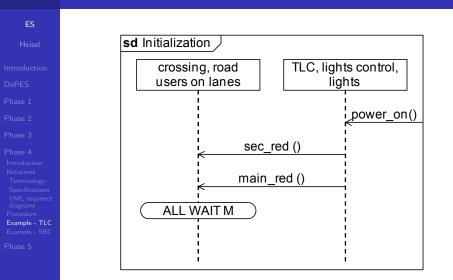

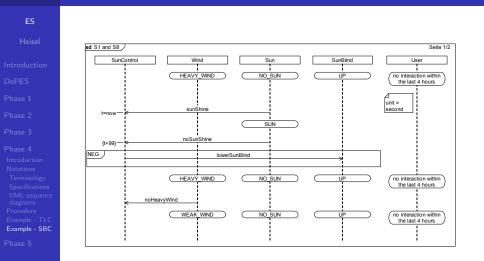

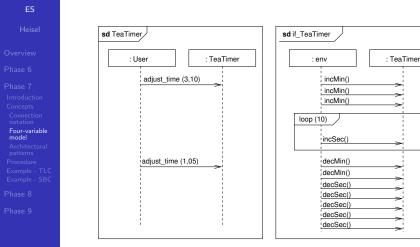

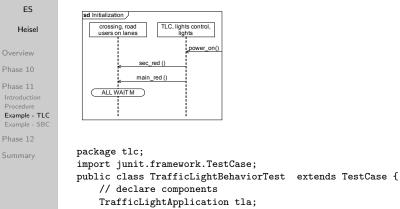

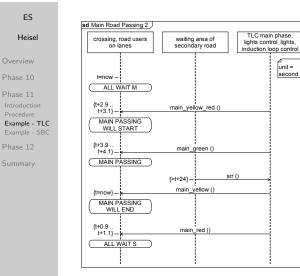

Phase 1

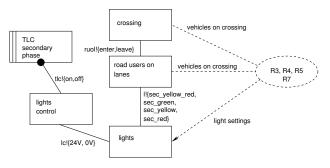

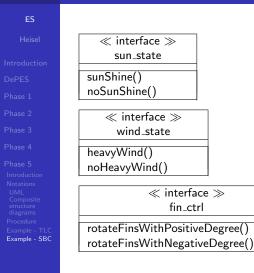

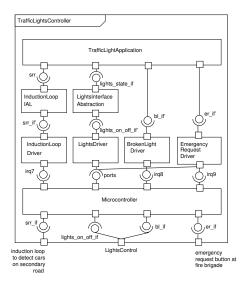

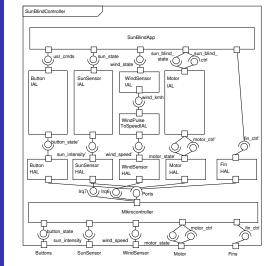

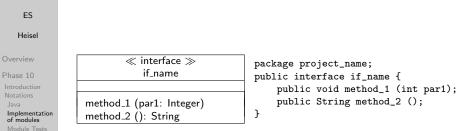

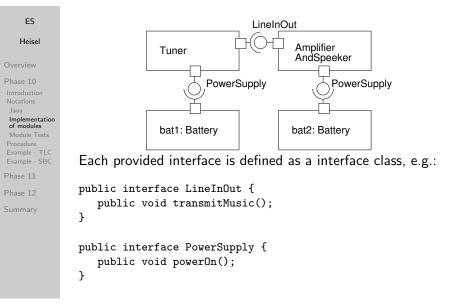

Phase 2

Phase 3

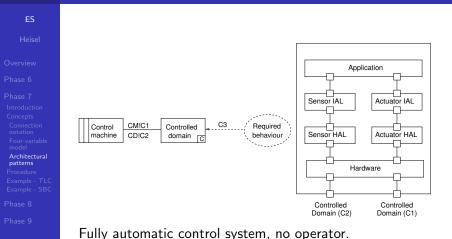

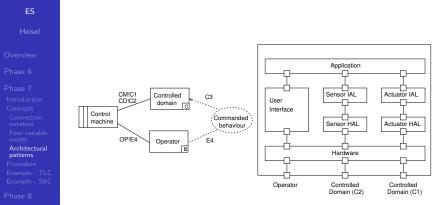

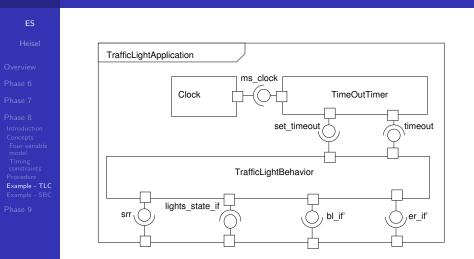

Phase 4

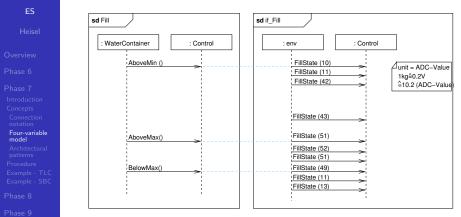

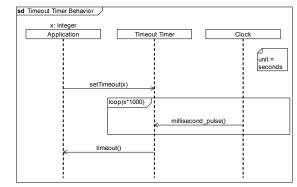

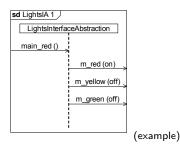

Phase 5

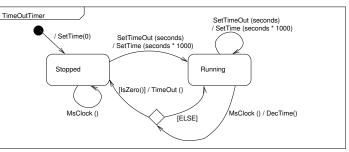

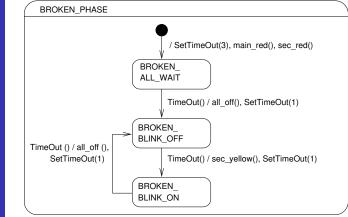

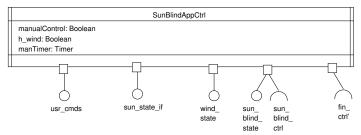

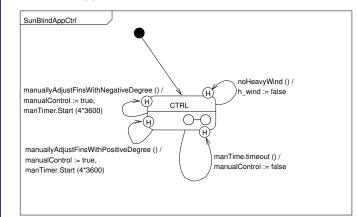

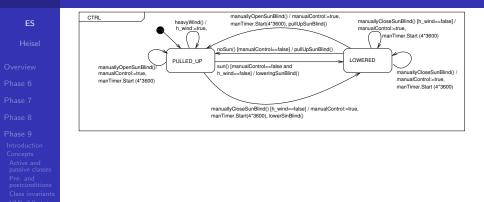

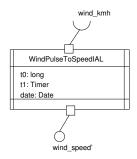

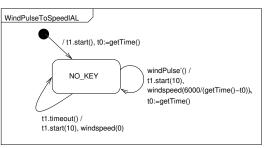

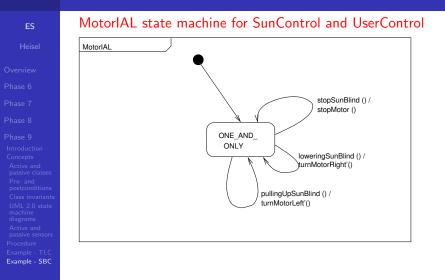

## Embedded Systems WS 08/09

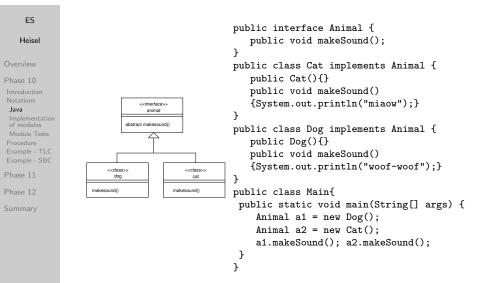

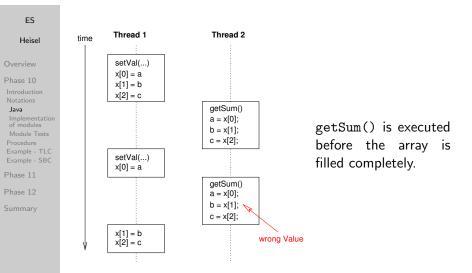

## Maritta Heisel Maritta.Heisel(AT)uni-duisburg-essen.de

Denis.Hatebur(AT)uni-duisburg-essen.de

University Duisburg-Essen – Faculty of Engineering Department of Computer Science Workgroup Software Engineering

## Content of lecture

#### ES

Heisel

#### Introduction

- DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

## Lecture

- Characteristics of embedded systems

- Development process for embedded systems

- Notations to be used in the development process

- If we have time: safety and security aspects of embedded systems, fault tolerance

## Practical part of the course

Development of a simple embedded system according to the development process

## Organizational issues of the course

### ES

### Heisel

### Introduction

- DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- Lecture: Tuesday 12–14, room BA 143

- Exercises and practical training: Tuesday, 14–16, room BA 143

beginning: Oct. 21, 2008

- Course material will be published under http://swe.uni-duisburg-essen.de/

## Organizational issues of the lab I

ES

Heisel

- Introduction

- DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- Set up groups of at least 3 and at most 5 students.

- Announce your group until 2008-10-19⇒ 1 email per group with names and matr.-numbers (denis.hatebur@uni-due.de)!

- Work on tasks and submit the group solution and all previous solutions in one .pdf-file until following Sunday 23:59. The email must include names and matr.-no of all members. The .pdf-file should include only the number of the group.

- If more than two solutions are submitted too late, the whole group will not pass the lab.

- All tasks must be processed.

## Organizational issues of the lab II

#### ES

### Heisel

### Introduction

- DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- To pass you have to attend all labs and submit all solutions in time (max. 2 exceptions).

- Everyone has to present the group solution at least (!) once.

- It must be indicated in the mail who performed the tasks and who performed the validation.

- All solutions will be published on the web.

## Literature I

#### ES

Heisel

- Introduction

- DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- Alan Burns and Andy Wellings: Real-Time Systems and Programming Languages.

Pearson Education, 2001.

- Denis Hatebur: A Pattern- and Component-Based Process for Embedded Systems Development. University Duisburg-Essen, 2006, http://swe.uni-duisburg-essen.de/intern/dpes.pdf

- David E. Simon: An Embedded Software Primer. Addison-Wesley 2004.

- Ahmad Ibrahim: Fuzzy Logic for Embedded Systems Applications (Embedded Technology), 2003

## Literature II

ES

Heisel

Introduction

DePES

Phase 1

Phase 2

Phase 3

Phase 4

Phase 5

Manfred Broy and Wolfgang Pree: Ein Wegweiser für Forschung und Lehre im Software-Engineering eingebetteter Systeme,

Informatik Spektrum, 18/2003, Volume 18.

Michael Jackson: Problem Frames. Analyzing and structuring software development problems. Addison Wesley, 2001.

Michael Jackson. Problems and requirements. In Proceedings of the IEEE Second International Symposium on Requirements Engineering. ACM Press, 1995.

Michael Jackson and Pamela Zave. Deriving specifications from requirements: an example. In *Proceedings 17th Int. Conf. on Software Engineering, Seattle, USA*, S. 15–24. ACM Press, 1995.

## Literature III

ES

- Heisel

- Introduction

- DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

Pamela Zave and Michael Jackson. Four dark corners of requirements engineering. ACM Transactions on Software Engineering and Methodology, 6(1):1–30, January 1997. Available at

http://www.research.att.com/~pamela/ori.html # fre

UML Superstructure Specification, v2.0 (709 Pages, 5.4 MB)

http://www.omg.org/docs/formal/05-07-04.pdf

- Laurent Doldi: UML 2.0 Illustrated. TMSO, 2003. http://www.tmso-systems.com

- M. Jeckle, C. Rupp, J. Hahn, B. Zengler, S. Queins: UML 2 glasklar. Hanser, 2004.

## Some definitions of embedded systems

ES

Heisel

- Introduction

- DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- Embedded systems are computer-based systems being part of products other than a computer (Broy and Pree, after Simon)

- Embedded systems are information technology systems embedded in an electro-mechanical environment. (Borusan and Weber)

- ... applications whose prime function is *not* that of information processing, but which nevertheless require information processing in order to carry out their prime function. (Ahmad Ibrahim)

About 99% of the worldwide production of microprocessors is used in embedded systems (Burns and Wellings).

# Typical tasks of embedded systems (Burns and Wellings)

#### ES

Heisel

#### Introduction

DePES

Phase 1

Phase 2

Phase 3

Phase 4

Phase 5

Process Control The computer interacts with its environment using sensors and actuators.

It controls the operation of the sensors and actuators to ensure that correct plant operations are performed at appropriate times.

Where necessary, analogue to digital (and vice versa) converters must be inserted between the controlled process and the computer.

Manufacturing The physical system consists of a variety of mechanical devices – such as machine tools, manipulators and conveyor belts – all of which need to be controlled and coordinated by the computer.

## Application domains of embedded systems

#### ES

Heisel

#### Introduction

- DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

## automotive

- aviation and space technology

- medical technology

- traffic guidance technology

- industrial automation

- telecommunications

- business

- entertainment

- household

## Examples for embedded systems

### Heisel

#### Introduction

- DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- anti-lock braking system (ABS)

- smartcard

- washing machine

- traffic light

- temperature control unit

- elevator control unit

- **.**..

## Characteristics of embedded systems I

#### ES

Heisel

#### Introduction

- DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- specialized for a particular purpose

- limited amount of resources (memory, power)

- high number of copies

- combination of hardware and software

- often security or safety critical

- connected via bus systems to other information technology systems

- larger embedded systems are often configurable

- faults in embedded software are expensive

## Characteristics of embedded systems II

#### ES

Heisel

#### Introduction

DePES

Phase 1

Phase 2

Phase 3

Phase 4

Phase 5

Embedded Software ...

- is usually reactive or continuous

- works on hardware with limited resources

- often has to fulfill safety or security requirements

- often fulfills timing requirements

- performs several tasks on one hardware

## Embedded vs. real-time systems

#### ES

Heisel

Introduction

DePES

Phase 1

Phase 2

Phase 3

Phase 4

Phase 5

Often used synonymously.

In contrast, we consider real-time systems to be a special kind of embedded systems:

A real-time system is any information processing activity of a system which has to respond to externally generated input stimuli within a finite and specified delay. (Burns and Wellings)

Real-time does not mean to be very fast. But if a real-time system does not react within the specified delay, this is considered to be a system fault.

Hard real-time system: delay in reaction may cause danger to life of people or assets.

### ES

Heisel

Introduction

#### DePES

Phase 1

Phase 2

Phase 3

Phase 4

Phase 5

## **Overview of development process (DePES)**

## Overview of development process (DePES) I

### ES

- Heisel

- Introduction

#### DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- 1. Describe system in use

- 2. Describe system to be built

- 3. Decompose problem

- 4. Derive a machine behavior specification for each subproblem

- 5. Design global system architecture

- 6. Derive specifications for all components of the global system architecture

- 7. Design an architecture for all programmable components of the global system architecture that will be implemented in software

## Overview of development process (DePES) II

#### ES

Heisel

#### Introduction

### DePES

- Phase 1

- Phase 2

- Phase 3

- Phase 4

- Phase 5

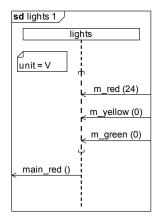

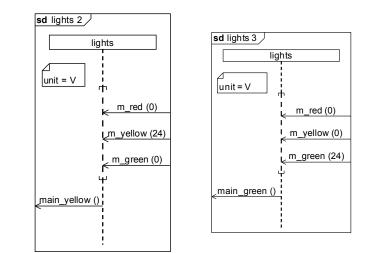

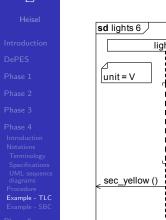

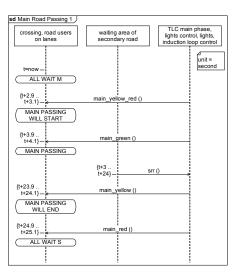

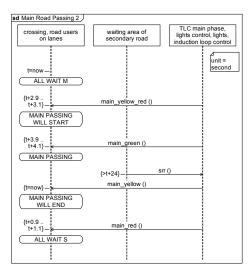

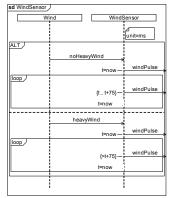

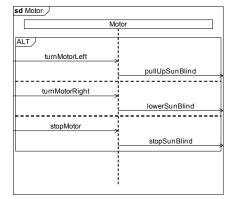

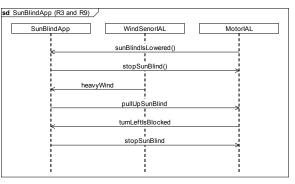

- 8. Specify the behavior of all components of all software architectures, using sequence diagrams

- 9. Specify the software components of all software architectures as state machines

- 10. Implement software components and test environment

- 11. Integrate and test software components

- 12. Integrate and test hardware and software

## Phase 1: Describe system in use

| ES           | input:      | informal description of the task            | natural language        |

|--------------|-------------|---------------------------------------------|-------------------------|

|              | output:     | context diagram of system in use            | Jackson without machine |

| Heisel       |             |                                             | domain                  |

|              |             | shortcomings                                | natural language        |

| Introduction |             | domain knowledge $D(F \land A)$             | natural language, (HTA, |

| DePES        |             |                                             | state machines)         |

| Phase 1      |             | glossary with definitions and designa-      | natural language        |

|              |             | tions                                       |                         |

| Phase 2      |             | list of possible development alternatives   | natural language        |

| Phase 3      | validation: | all domains and phenomena in the con-       |                         |

| Phase 4      |             | text diagram must be described.             |                         |

|              |             | the context diagram must contain all        |                         |

| Phase 5      |             | domains necessary to describe the short-    |                         |

|              |             | comings.                                    |                         |

|              |             | shortcomings must be stated using ele-      |                         |

|              |             | ments of the domain knowledge descrip-      |                         |

|              |             | tion.                                       |                         |

|              |             | the glossary contains the notions used      |                         |

|              |             | in D.                                       |                         |

|              |             | each entry in the list of possible develop- |                         |

|              |             | ment alternatives must consider at least    |                         |

|              |             | one of the shortcomings.                    |                         |

|              |             |                                             |                         |

## Phase 2: Describe system to be built

| ES                  | input:                                | all results of Phase 1                        | Jackson/ natural lan-   |

|---------------------|---------------------------------------|-----------------------------------------------|-------------------------|

|                     |                                       |                                               | guage                   |

| Heisel              | output:                               | system mission statement                      | natural language        |

|                     |                                       | selected development alternatives             | natural language        |

| ntroduction         |                                       | context diagram of system to be built         | ext. Jackson            |

| DePES               |                                       | changed domain knowledge $D$ ( $F \land A$ )  | natural language, (HTA, |

| Phase 1             |                                       |                                               | state machines)         |

|                     |                                       | initial set of requirements R <sub>init</sub> | natural language        |

| <sup>p</sup> hase 2 |                                       | requirements $R$ to be implemented            | natural language        |

| Phase 3             | validation:                           | only the limited set of operators is applied  |                         |

| <sup>o</sup> hase 4 |                                       | on the context diagram of system in use       |                         |

|                     |                                       | to derive the context diagram of system to    |                         |

| Phase 5             |                                       | be built                                      |                         |

|                     |                                       | system mission statement must address         |                         |

|                     |                                       | the shortcomings or refer to domain knowl-    |                         |

|                     |                                       | edge of the system in use                     |                         |

|                     |                                       | domains and phenomena in the context di-      |                         |

|                     |                                       | agram and in $R$ and $D$ must be consistent   |                         |

|                     |                                       | R must be a subset of R <sub>init</sub>       |                         |

|                     |                                       | changes in the domain knowledge must be       |                         |

|                     |                                       | justified by the requirements                 |                         |

|                     |                                       | $D \wedge R$ are non-contradictory            |                         |

|                     | · · · · · · · · · · · · · · · · · · · |                                               |                         |

## Phase 3: Decompose problem

| ES           |             |                                 |              |

|--------------|-------------|---------------------------------|--------------|

|              | input:      | requirements $R$ to be imple-   | natural lan- |

| Heisel       |             | mented of Phase 2               | guage        |

| Introduction |             | domain knowledge D of           | natural lan- |

| DePES        |             | Phase 2                         | guage        |

| Phase 1      |             | context diagram of Phase 2      | ext. Jackson |

| Phase 2      | output:     | set of problem diagrams with    | Jackson with |

| Phase 3      |             | associated set of requirements  | dot-notation |

| Phase 4      |             | expression of the subproblem    | grammar      |

| Phase 5      |             | relationships                   |              |

|              | validation: | consistent with context dia-    |              |

|              |             | gram of Phase 2                 |              |

|              |             | requirements $R$ of Phase 2     |              |

|              |             | must be treated in at least one |              |

|              |             | subproblem                      |              |

|              |             |                                 |              |

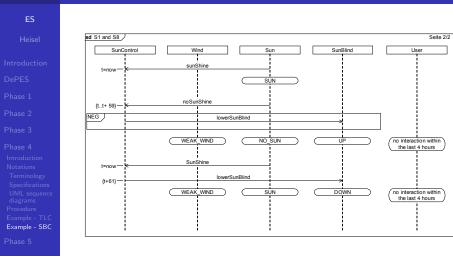

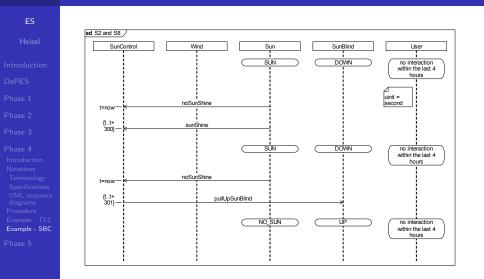

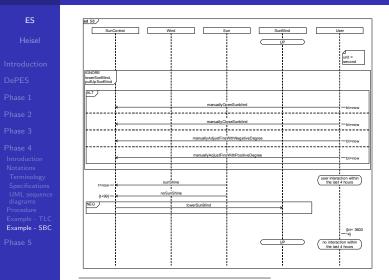

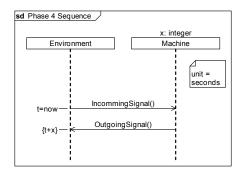

# Phase 4: Derive a machine behavior specification for each subproblem $P_i$

| input:     | requirements R from Phase 2                       | natural language  |

|------------|---------------------------------------------------|-------------------|

|            | domain knowledge D from Phase 2                   | natural language  |

|            | problem diagram for $P_i$ from Phase 3            | Jackson with dot- |

|            |                                                   | notation          |

| on output: | specification $S_{P_i}$ of machine to construct   | natural language  |

|            | sequences of interactions with annotated states   | sequence diagrams |

|            | for the domains in the environment, expressing    | with annotated    |

|            | $R_{P_i}$ and $D_{P_i}$                           | states            |

|            | sequences of interactions on initialization       | sequence diagram  |

|            |                                                   | with annotated    |

|            |                                                   | states            |

| validation | $D \wedge S_{P_i}$ are non-contradictory          |                   |

|            | $D \wedge S_{P_i} \Longrightarrow R_{P_i}$        |                   |

|            | all requirements must be captured                 |                   |

|            | in the sequence diagrams refined phenomena of     |                   |

|            | the problem diagrams are used as signals          |                   |

|            | direction of signals must be consistent with con- |                   |

|            | trol of shared phenomena                          |                   |

|            | signals must connect domains as connected in      |                   |

|            | problem diagram                                   |                   |

|            | the relationships of Phase 3 must be consistent   |                   |

|            | with the states                                   |                   |

## Phase 5: Design global system architecture I

| ES    | input:  | context diagram from Phase 2                 | ext. Jackson      |

|-------|---------|----------------------------------------------|-------------------|

|       |         | problem diagrams from Phase 3                | Jackson with dot- |

|       |         |                                              | notation          |

|       |         | sequences of interactions between machine    | sequence diagrams |

| DePES |         | and environment of all subproblems from      |                   |

|       |         | Phase 4                                      |                   |

|       |         | expression of the subproblem relationships   | grammar           |

|       |         | from Phase 3                                 |                   |

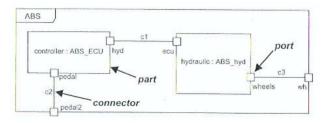

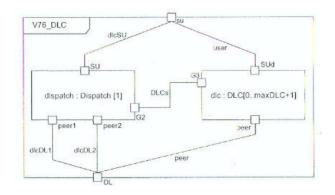

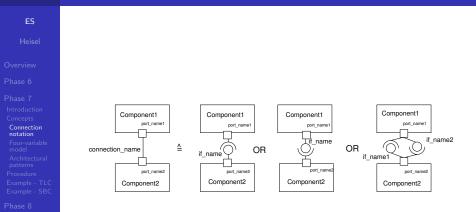

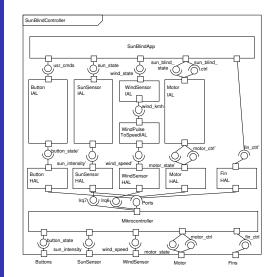

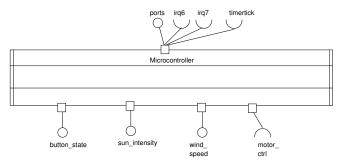

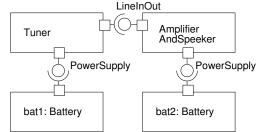

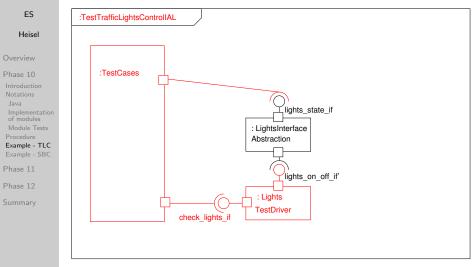

|       | output: | system architecture                          | composite struc-  |

|       |         |                                              | ture diagram      |

|       |         | perhaps subcomponents (recursively)          | composite struc-  |

|       |         |                                              | ture diagrams     |

|       |         | purpose of each component                    | natural language  |

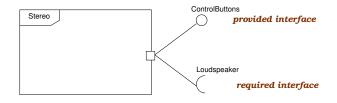

|       |         | specification of external interfaces         | interface classes |

|       |         | specification of interfaces between the com- | interface classes |

|       |         | ponents                                      |                   |

|       |         | technical description of hardware interfaces | natural language, |

|       |         |                                              | figures           |

|       |         | expression of the subproblem relationships   | grammars          |

|       |         | for all components                           |                   |

## Phase 5: Design global system architecture II

| ES           |                                       |                                            |  |

|--------------|---------------------------------------|--------------------------------------------|--|

| ES           | validation: a                         | all machine interfaces of the problem dia- |  |

| Heisel       | 8                                     | grams must be captured                     |  |

|              | t                                     | the signals in the sequence diagrams must  |  |

| Introduction | ł                                     | be the same as the signals in the external |  |

| DePES        |                                       | nterfaces                                  |  |

| Phase 1      | t                                     | to each programmable component at least    |  |

| Phase 2      | 0                                     | one problem diagram must be associated     |  |

| Phase 3      | e                                     | each problem diagram must be associated    |  |

|              | t                                     | to at least one component                  |  |

| Phase 4      | a                                     | all domains in the problem diagrams being  |  |

| Phase 5      | l l                                   | part of the machine must be associated to  |  |

|              | a                                     | a component                                |  |

|              | e                                     | each machine domain in the context dia-    |  |

|              | E E E E E E E E E E E E E E E E E E E | gram must occur in the architecture        |  |

|              | 4                                     | purpose must be consistent with the asso-  |  |

|              | 0                                     | ciated requirements                        |  |

|              | t                                     | the grammar for each component must de-    |  |

|              | s                                     | scribe a subset of the grammar in Phase 3  |  |

# Phase 6: Derive specifications for all components of the global system architecture

. . . . . . . . . . . . . . . . . . .

DePES

Phase 1

Phase 2

Phase 3

Phase 4

Phase 5

## For each subproblem:

| input:      | architecture from Phase 5                        | composite structure   |

|-------------|--------------------------------------------------|-----------------------|

|             |                                                  | diagrams              |

|             | interface specifications from Phase 5            | interface classes     |

|             | subcomponents (if defined) from Phase 5          | composite structure   |

|             |                                                  | diagrams              |

|             | sequences of interactions from Phase 4           | sequence diagrams     |

|             |                                                  | with annotated states |

|             |                                                  | or existing technical |

|             |                                                  | documentation         |

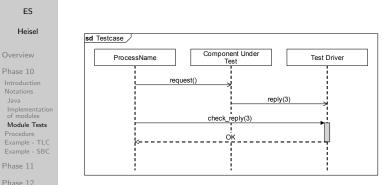

| output:     | interface behavior of all components (test spec- | sequence diagrams     |

|             | ification)                                       | with annotated states |

| validation: | sequence diagrams together must describe the     |                       |

|             | same interface behavior as in Phase 4            |                       |

|             | all signals in the interface classes of Phase 5  |                       |

|             | must be used in at least one sequence diagram    |                       |

|             | direction of signals must be consistent with the |                       |

|             | required and provided interfaces of Phase 5      |                       |

|             | signals must connect components as connected     |                       |

|             | in the system architecture of Phase 5            |                       |

|             | it must be possible to map the new states to the |                       |

|             | states of Phase 4                                |                       |

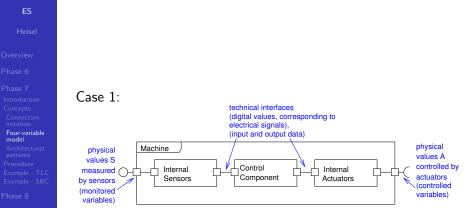

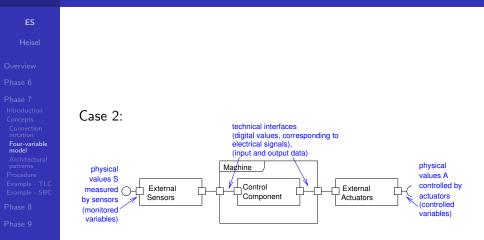

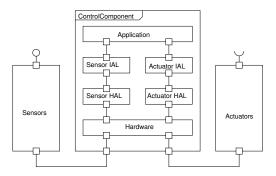

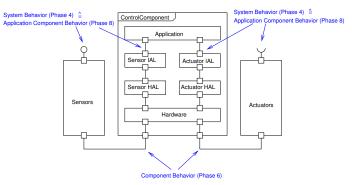

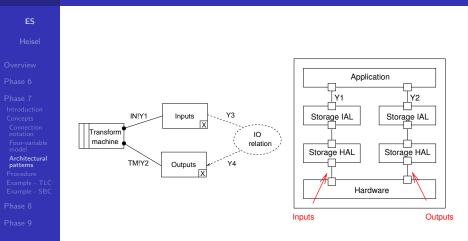

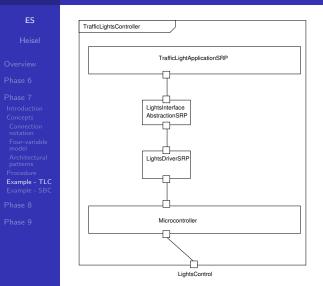

# Phase 7: Design a software architecture for all components of the global system architecture

| 50           | Lin muster  | alahal watawa anahita atawa ƙwara Dharas F                  | dia                       |

|--------------|-------------|-------------------------------------------------------------|---------------------------|

| ES           | input:      | global system architecture from Phase 5                     | composite structure dia-  |

|              |             |                                                             | gram                      |

| Heisel       |             | problem diagrams from Phase 3                               | Jackson with dot-         |

|              |             |                                                             | notation                  |

| Introduction |             | interface specifications from Phase 5                       | interfaces classes        |

| DePES        |             | relationships between subproblems specified in Phase 5      | grammars                  |

|              |             | possibly reusable components from other projects            | active or passive classes |

| Phase 1      |             | (Phase 9)                                                   | with interface classes    |

| Phase 2      |             | machine behavior specifications from Phase 4                | sequence diagrams with    |

| Phase 3      |             |                                                             | annotated states          |

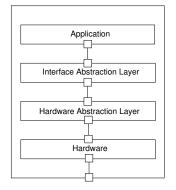

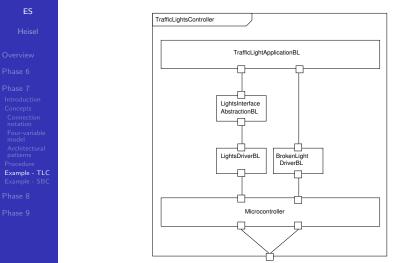

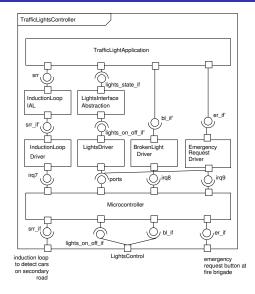

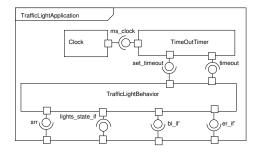

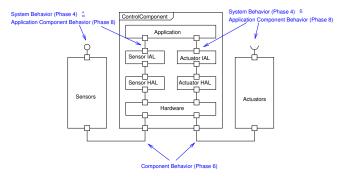

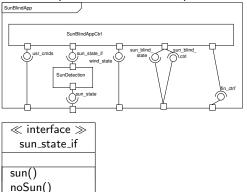

| r liase 5    | output:     | layered software architecture for each subproblem           | composite structure dia-  |

| Phase 4      |             |                                                             | grams                     |

| Phase 5      |             | merged layered software architecture (with subcompo-        | composite structure dia-  |

| 1 11450 0    |             | nents)                                                      | grams                     |

|              |             | purpose of each software component                          | natural language          |

|              |             | specification of interfaces between software components     | interface classes         |

|              | validation: | if no instantiation of architectural patterns: consistent   |                           |

|              |             | with problem diagram                                        |                           |

|              |             | signals of Phase 4 sequence diagrams are interfaces of      |                           |

|              |             | the application layer                                       |                           |

|              |             | direction of all signals consistent to each other and input |                           |

|              |             | external interfaces must be consistent with the interfaces  |                           |

|              |             | of the system architecture developed in Phase 5             |                           |

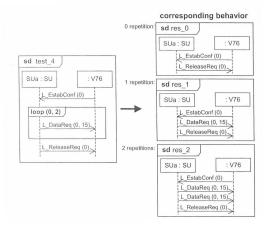

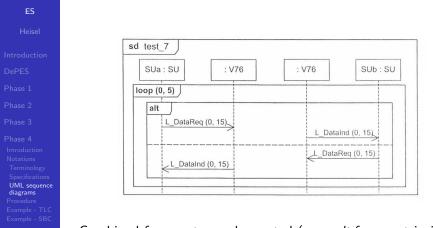

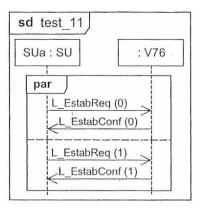

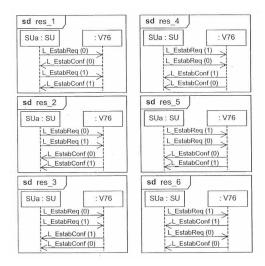

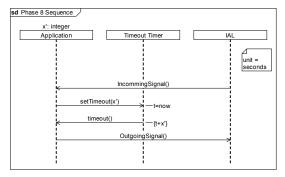

# Phase 8: Specify the behavior of all components of all software architectures, using sequence diagrams

ES

### Heisel

DePES

## For each subproblem:

| input:      | software architectures from Phase 7              | composite     | structure  |

|-------------|--------------------------------------------------|---------------|------------|

|             |                                                  | diagrams      |            |

|             | interface specifications from Phase 7            | interface cla | isses      |

|             | system behavior from Phase 4                     | sequence      | diagrams   |

|             |                                                  | with annota   | ted states |

|             | interface behavior of all programmable compo-    | sequence      | diagrams   |

|             | nents from Phase 6                               | with annota   | ted states |

| output:     | interface behavior of all software components    | sequence      | diagrams   |

|             | (test specification)                             | with annota   | ted states |

| validation: | all sequence diagrams together must describe     |               |            |

|             | the same interface behavior as in Phase 6        |               |            |

|             | all signals in the interfaces classes of Phase 7 |               |            |

|             | must be used in at least one sequence diagram    |               |            |

|             | direction of signals must be consistent with the |               |            |

|             | required and provided interfaces of Phase 7      |               |            |

|             | signals must connect components as connected     |               |            |

|             | in the software architecture of Phase 7          |               |            |

|             | it must be possible to map any new states to the |               |            |

|             | states of Phase 6                                |               |            |

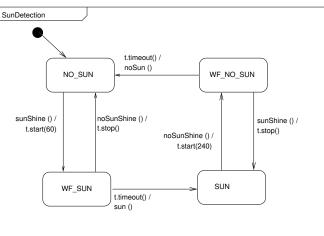

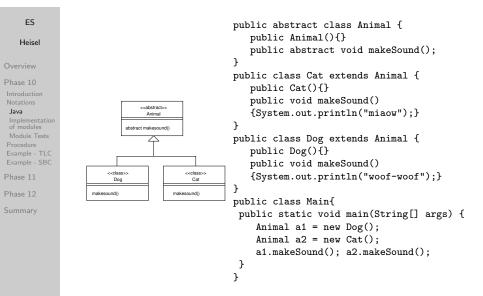

# Phase 9: Specify the software components of all software architectures as state machines

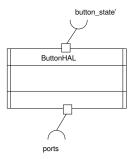

| ES    | input:     | interface behavior from Phase 8              | sequence diagrams  |

|-------|------------|----------------------------------------------|--------------------|

|       |            |                                              | with annotated     |

|       |            |                                              | states             |

|       |            | relationships between subproblems speci-     | grammars           |

|       |            | fied in Phase 5                              | -                  |

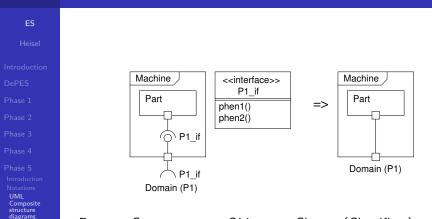

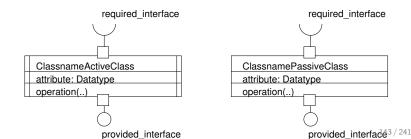

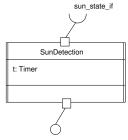

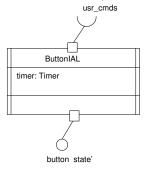

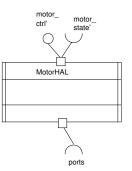

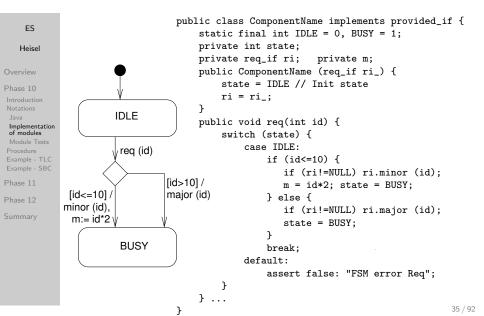

| DePES | output:    | component overview description with refer-   | class diagram with |

|       |            | ences to interface classes                   | ports, sockets and |

|       |            |                                              | lollipops          |

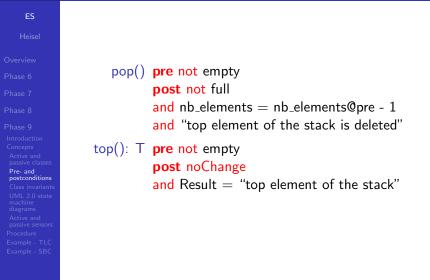

|       |            | data types and operations                    | class diagrams     |

|       |            | defined using pre- and postconditions        | formulas or natu-  |

|       |            |                                              | ral language       |

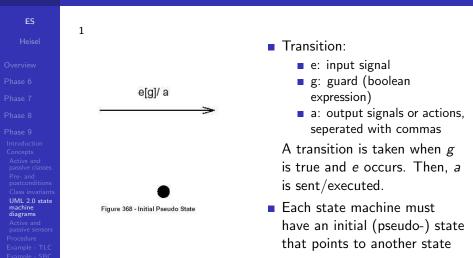

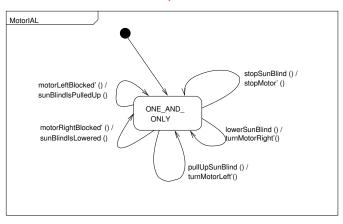

|       |            | state machines                               | state machine dia- |

|       |            |                                              | grams              |

|       |            | invariants                                   | formulas or natu-  |

|       |            |                                              | ral language       |

|       | validation | consistent with interface behavior from      |                    |

|       |            | Phase 8                                      |                    |

|       |            | completeness of state machines (implies      |                    |

|       |            | error-cases for user-interaction)            |                    |

|       |            | a class must be active if it contains an ac- |                    |

|       |            | tive class or a timer                        |                    |

|       |            |                                              |                    |

# Phase 10: Implement software components and test environment

| ES           |         |                        |

|--------------|---------|------------------------|

| Heisel       |         |                        |

| Introduction | input:  | software componen      |

| DePES        | input.  | Phase 8                |

| Phase 1      |         | specification of merg  |

| Phase 2      |         | Phase 9                |

| Phase 3      | output: | test software for soft |

| input:      | software component behavior from      | sequence diagrams     |  |  |  |

|-------------|---------------------------------------|-----------------------|--|--|--|

|             | Phase 8                               | with annotated states |  |  |  |

|             | specification of merged components of | different notations   |  |  |  |

|             | Phase 9                               |                       |  |  |  |

| output:     | test software for software components | programming lan-      |  |  |  |

|             |                                       | guage or test lan-    |  |  |  |

|             |                                       | guage                 |  |  |  |

|             | implemented software components       | programming lan-      |  |  |  |

|             |                                       | guage                 |  |  |  |

| validation: | run tests                             | test results          |  |  |  |

## Phase 11: Integrate and test software components

ES

#### Heisel

Introduction

#### DePES

Phase 1

Phase 2

Phase 3

Phase 4

| input:      | global software architecture from  | composite structure dia-   |  |

|-------------|------------------------------------|----------------------------|--|

|             | Phase 7                            | grams                      |  |

|             | software behavior from Phase 6     | sequence diagrams with an- |  |

|             | notated states                     |                            |  |

|             | implemented software compo-        | programming language       |  |

|             | nents from Phase 10                |                            |  |

| output:     | implemented software               | programming language       |  |

|             | test software for integrated soft- | programming language or    |  |

|             | ware                               | test language              |  |

| validation: | run tests                          | test results               |  |

## Phase 12: Integrate and test hardware and software

ES

Heisel

Introduction

DePES

Phase 1

Phase 2

Phase 3

Phase 4

| input:      | system architecture from Phase 5 | composite structure dia-   |  |

|-------------|----------------------------------|----------------------------|--|

|             |                                  | gram                       |  |

|             | system specifications from       | sequence diagrams with an- |  |

|             | Phase 4                          | notated states             |  |

|             | expression of the subproblem re- | grammar                    |  |

|             | lationships from Phase 3         |                            |  |

|             | implemented software from        | programming language       |  |

|             | Phase 11                         |                            |  |

| output:     | integrated system                | machine                    |  |

|             | acceptance test cases            | test system and/or test    |  |

|             |                                  | plans                      |  |

| validation: | run tests                        | test results               |  |

## Phase 1: Describe system in use

#### ES

Heisel

- Introduction

- DePES

- Introduction

- Notations Terminology Context diagrams R, D & S Summary Procedure

- Example SB

- Phase 2

- Phase 3

- Phase 4

- Phase 5

## 1. Describe system in use

- 2. Describe system to be built

- 3. Decompose problem

. . .

- 4. Derive machine behavior specification for each subproblem

- 5. Design global system architecture

- 6. Derive specifications for all components of the global system architecture

- 7. Design a software architecture for all components of the global system architecture that should be implemented in software

- 8. Specify the behavior of all components of all software architectures, using sequence diagrams

## Phase 1: Describe system in use

| ES                     | input:      | informal description of the task            | natural language        |

|------------------------|-------------|---------------------------------------------|-------------------------|

|                        | output:     | context diagram of system in use            | Jackson without machine |

| Heisel                 |             |                                             | domain                  |

|                        |             | shortcomings                                | natural language        |

| Introduction           |             | domain knowledge $D(F \land A)$             | natural language, (HTA, |

| DePES                  |             |                                             | state machines)         |

| Phase 1                | -           | glossary with definitions and designa-      | natural language        |

| Introduction           |             | tions                                       |                         |

| Notations              |             | list of possible development alternatives   | natural language        |

| Terminology<br>Context | validation: | all domains and phenomena in the con-       |                         |

| diagrams               |             | text diagram must be described.             |                         |

| R, D & S<br>Summary    |             | the context diagram must contain all        |                         |

| Procedure              |             | domains necessary to describe the short-    |                         |

| Example - TLC          |             | comings.                                    |                         |

| Example - SBC          |             | 0                                           |                         |

| Phase 2                |             | shortcomings must be stated using ele-      |                         |

|                        |             | ments of the domain knowledge descrip-      |                         |

| Phase 3                |             | tion.                                       |                         |

| Phase 4                |             | the glossary contains the notions used      |                         |

| Phase 5                |             | in D.                                       |                         |

| Phase 5                |             | each entry in the list of possible develop- |                         |

|                        |             | ment alternatives must consider at least    |                         |

|                        |             | one of the shortcomings.                    |                         |

|                        |             |                                             |                         |

## Notations and concepts

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminolog Context diagrams R, D & S

Procedure

Example - SE

Phase 2

Phase 3

Phase 4

- Terminology

- Context diagrams

- Requirements

- Domain knowledge

- Glossary

- Specification

## Terminology: System, machine and environment I

#### ES

#### Heisel

- Introduction

- DePES

#### Phase 1 Introduction Notations Terminology Context diagrams R D & S

- Summary Procedure Example - TL Example - SE

- Phase 2

- Phase 3

- Phase 4

- Phase 5

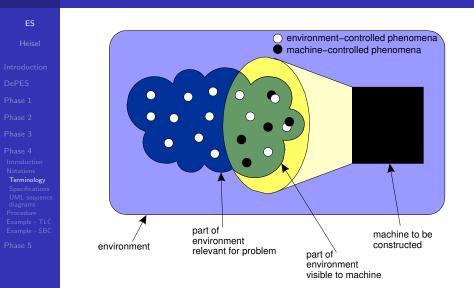

- A system consists of a machine and its environment.

- System is a recursive term: A system can consist of other systems.

- The machine is the system to be built.

- Each machine acts in an environment

## Terminology: System, machine and environment II

ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure

Example - T Example - S

Phase 2

Phase 3

Phase 4

Phase 5

**Goal**: Design of a system with specified characteristics *Example*: An elevator should enable persons in a building to get from one floor to another.

Components of the system:

environment: part of "real world" relevant for the problem Example: floors, persons, cage, doors, engine, buttons, sensors, ...

machine: controlling software and suitable hardware

Properties of the environment are fixed. We have to build the machine, so that it realizes the desired properties of the system.

## Terminology: Phenomena I

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology

diagrams R, D & S Summary Procedure Example - TLO Example - SBO

Phase 2

Phase 3

Phase 4

Phase 5

State and behavior of the environment can be described by phenomena. Examples:

### Elevator

Person presses button, expects, that the elevator arrives.

### Bank

Client gives withdrawal instruction, expects a withdrawal.

Machine can interact with the environment by

- observing certain phenomena (input) ( $\rightarrow$  sensors)

- causing certain phenomena (output) (→ actuators)

# Terminology: Phenomena II

#### ES

### Heisel

#### Introduction

DePES

#### Phase 1 Introduction Notations Terminology

Context diagrams R, D & S Summary Procedure Example - T Example - SI

Phase 2

Phase 3

Phase 4

Phase 5

### Phenomena

- are actions/events/operations that occur in the environment

- are important for expressing statements

- can be observed or controlled by the environment or the machine, respectively

### Examples:

- waiting in front of the elevator

- pressing the button inside the elevator

- elevator door closes

# Terminology: Control of phenomena

ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL Example - SB

Phase 2

Phase 3

Phase 4

Phase 5

1. Controlled by the environment, not observable by the machine

Example: waiting in front of the elevator

- 2. Controlled by the environment, observable by the machine Example: *pressing the button inside the elevator*

- 3. Controlled by the machine, observable by the environment Example: *elevator door closes*

The category "controlled by the machine, not observable by the environment" is not considered in this phase, since internal phenomena of the machine do not belong to the requirements.

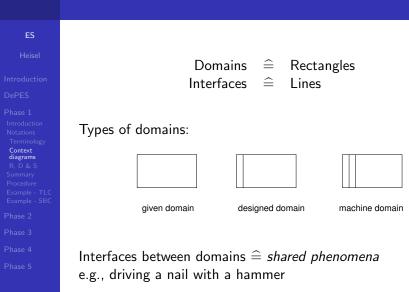

### Context diagrams

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL Example - SE

Phase 2

Phase 3

Phase 4

Phase 5

- Distinction between environment and machine

- Representation of the connections between environment and machine

- Structuring the environment into a machine and (usually several) problem domains

- Connections between domains

- Represent the world, when the machine is in operation

### Context diagrams - Notation

# Context diagram example: patient monitoring system

#### ES

Heisel

Introductio

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL( Example - SB(

Phase 3

Phase 4

Phase 5

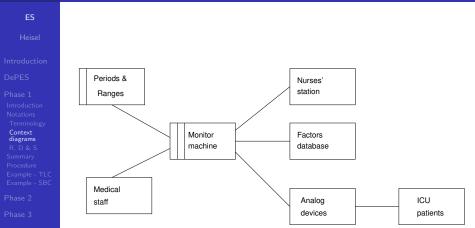

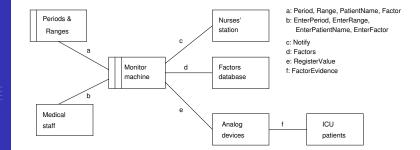

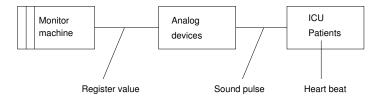

A patient monitoring program is required for the intensive-care unit of a hospital. Each patient is monitored by an analog device which measures factors such as pulse, temperature, blood pressure, and skin resistance.

The program reads these factors on a periodic basis (specified for each patient) and stores the factors in a database. For each patient, safe ranges for each factor are also specified by medical staff.

If a factor falls outside a patient's safe range, or if an analog device fails, then the nurses' station is notified.

# Related (provisional) Context Diagram

### Context Diagram of a Problem

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLI Example - SB Phase 2

Phase 3

Phase 4

Phase 5

- forms the basis for structuring and analyzing the problem

- shows all domains that need to be taken into consideration

- everything that does not appear in the context diagram, is not considered

$\implies$  careful selection of domains necessary!

# Example: different possibilities for the database domain

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL Example - SB

Phase 2

Phase 3

Phase 4

Phase 5

- Factor database as *given* domain

- $\implies$  it already exists, does not have to be designed

- If it were part of the task:

Only sensible, if the database is also used by other systems.

• Otherwise: Database as part of the machine that is to be constructed, *no separate domain* in the context diagram

### Context Diagram – Complete Notation

#### ES

Heisel

#### Introduction

#### DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLi Example - SBi Phase 2 Phase 3

- Phase 4

- Phase 5

### Write down shared phenomena at the connecting lines

### Extended Context Diagrams

#### ES

### Heisel

Introduction

#### DePES

Phase 1 Introduction Notations Terminology **Context diagrams** R, D & S Summary Procedure Example - TL Example - SE Phase 2

User edit Client requests Network requests, config Administrator settings Client B Client Server

Systems with more than one machine are necessary, when the machines are physically distributed (e.g., Client-Server Systems). Therefore, Jackson's context diagrams are extended to allow more than one machine domain.

### Context Diagram – Connection Domains I

#### ES

#### Heisel

#### Introduction

#### DePES

#### Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL Example - SB Phase 2

#### DI 4

Phase 5

Patients and the machine are not directly connected, but indirectly through a causality chain:

### Context Diagram – Connection Domains II

ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL Example - SB Phase 2

Phase 3

Phase 4

Phase 5

Shared phenomena in context diagrams are abstractions of real phenomena, e.g. by

omitting properties that are not relevant for the purpose at hand at that moment

e.g., the event Notify surely has arguments

treat complex episode of interaction as an instantaneous event

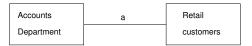

Care must be taken in the latter abstraction, as the following example taken from retail shows:

### Context Diagram – Connection Domains III

ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL Example - SE Phase 2

rnase o

Phase 4

Phase 5

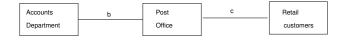

If issuing an invoice and payment are carried out via postal mail, then the above mentioned context diagram would represent a (too great) abstraction of what actually happens :

b: SendBill, ReceivePayment

c: SendPayment, ReceiveBill

The phenomena *Bill* and *Pay* are in fact no shared phenomena of *AccountsDepartment* and *RetailCustomers*, since the mail acts as intermediary, which causes delays and uncertainties.  $\Rightarrow$  We need the *Post Office* as a connection domain.

### Context Diagram – Connection Domains IV

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL Example - SB

Phase 3

Phase 4

Phase 5

Connection domains are necessary, if

- they are explicitly mentioned in the requirements, such as analog devices in the patient monitoring system

- may cause delays, that cannot be ignored, as shown in the retail example

- the transmission via the connection domain is unreliable, e.g., failure of an analog device.

# Setting up Context Diagrams

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL( Example - SB

mase 2

Phase 3

Phase 4

Phase 5

### Problem: circularity:

- It can only be decided on the context, if an overview of the problem is available.

- A problem is only properly known, if its embedding in environment is known.

$\Longrightarrow$  Iterative analysis of problem context and requirements

# R, D & S – Requirements and specification I

#### ES

Heisel

- Introduction

- DePES

- Phase 1 Introduction Notations Terminology Context diagrams **R**, D & S Summary Procedure Example - Th

- Phase 2

- Phase 3

- Phase 4

Phase 5

- Known:

- (1) Fixed characteristics of the environment (domain knowledge)

- (2) Desired characteristics of the system (requirements)

- Clear: Machine must close the "gap" between (1) and (2)

- Searched: specification of the machine "How should the machine act, so that the system fulfills the requirements?"

Requirements describe the environment, the way it should be, after the machine is integrated.

# R, D & S – Functional vs. non-functional requirements

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams **R**, D & S Summary Procedure Example - TLC Example - SBC Phase 2 Phase 3

Phase 4

Phase 5

- Functional requirements: state how the system should act

Non-functional manipumentation account multitude

- Non-functional requirements: concern quality characteristics such as efficiency or user-friendliness

fulfillment of functional requirements  $\hat{=}$  correctness fulfillment of non-functional requirements  $\hat{=}$  ???

Decisions on fulfillment of non-functional requirements need the definition of separate criteria! In the following: only functional requirements

### R & D – Types of statements

ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams **R, D & S** Summary Procedure Example - TL Example - SB

Dhaan 2

Phase 4

Phase 5

Indicative Statements describe the environment irrespective of how the machine is built.

Other notion: domain knowledge.

Example: a door cannot be open and closed at the same time.

Optative statements describe the environment, in the way we would expect it after the machine is integrated. Example: After the button was pressed, the elevator stops at the corresponding floor.

Note: Statements are characterized by being true or false.

Requirements are thus optative statements.

# D – Types of domain knowledge

#### ES

Heisel

Introductio

DePES

Phase 1 Introduction Notations Terminology Context diagrams **R, D & S** Summary Procedure Example - TL Example - SE Phase 2

Phase 5

Facts describe conditions that are always fulfilled.

Example: When the motor turns right, the elevator moves to a higher floor

(This fact is needed to transform the requirement "Move to another floor" into a specification with phenomena visible to the machine (turn motor right).)

Assumptions describe conditions that are needed, so that the requirements are satisfiable.

Example: When the elevator reaches my floor, I enter (This assumption is needed for fulfilling the requirement that the elevator carries all waiting persons to their destination.)

# D – Types of domain knowledge: Facts

#### ES

Heisel

- Introduction

- DePES

- Phase 1 Introduction Notations Terminology Context diagrams **R, D & S** Summary Procedure Example - SE

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- When it rains, the sensor gets wet.

- A wet sensor has an impedance below 100 Ω, and a dry sensor has an impedance above 200 Ω.

- When a airplane is on the ground and it is not stopped the wheels are turning. (?)

- When a car passes the sensor a pulse is generated.

# D – Types of domain knowledge: Assumptions

#### ES

### Heisel

- Introduction

- DePES

- Phase 1 Introduction Notations Terminology Context diagrams **R**, D & S Summary Procedure Example - TI Example - SE

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- In case of fire the user presses the emergency button.

- The cars passing the sensor have a height of more than one meter.

- The button is pressed for more than 0.5 seconds.

### R & S – Specifications

- are descriptions that are sufficient for building the machine

- are **implementable** requirements

- correctness condition:

If the machine fulfills the specification, the system fulfills the requirements.  $S \land D \Rightarrow R$

### R & S – Specifications vs. requirements

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams **R, D & S** Summary Procedure Example - SE Phase 2

Phase 3

Phase 4

Phase 5

Requirements are NOT implementable, if they

- constrain actions that are controlled by the environment Example: The elevator is not be overloaded.

- refer to actions that are not observable by the machine Example: The elevator should go to a floor where people are waiting.

- express conditions that can only be decided in the future Example: As soon as a user has dialed the last digit, he receives the dial tone, the busy signal, or the announcement "number not assigned".

### Glossary – Designations

ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams **R**, **D** & **S** Summary Procedure Example - TI Example - SI

Phase 2

Phase 3

Phase 4

Phase 5

System descriptions require designations as basic vocabulary

- Each designation has

- (1) a name

- (2) a (detailed) explanation

Example.: A *student* is somebody who is enrolled at a university.

• With designations, we can form statements, e.g.

```

\forall s : student \bullet \exists l : lecture \bullet enrolled(s, l)

```

(assuming that designations of *lecture* and *enrolled* are available)

### Glossary – Definitions

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams **R, D & S** Summary Procedure Example - TL Example - SD

Phase 3

Phase 4

Phase 5

expand the available vocabulary, but not its expressivenesscan be absurd or useless, but not false

A defined notion can always be replaced by its definition. Example:

$$student(s) \cong \exists I : lecture \bullet enrolled(s, I)$$

### Summary of the terminology

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL Example - SE

Phase 2

Phase 3

Phase 4

Phase 5

You should have learned the following notions:

- machine

- environment

- designation

- definition

- indicative statement

- optative statement

- assumption

- fact

- shared phenomenon (action / event / operation)

- requirement

- specification

### Phase 1: Describe system in use

| ES                             | input:      | informal description of the task            | natural language        |

|--------------------------------|-------------|---------------------------------------------|-------------------------|

|                                | output:     | context diagram of system in use            | Jackson without machine |

| Heisel                         |             |                                             | domain                  |

|                                |             | shortcomings                                | natural language        |

| Introduction                   |             | domain knowledge $D(F \land A)$             | natural language, (HTA, |

| DePES                          |             |                                             | state machines)         |

| Phase 1                        |             | glossary with definitions and designa-      | natural language        |

| Introduction                   |             | tions                                       |                         |

| Notations                      |             | list of possible development alternatives   | natural language        |

| Terminology<br>Context         | validation: | all domains and phenomena in the con-       |                         |

| diagrams                       |             | text diagram must be described.             |                         |

| R, D & S<br>Summary            |             | the context diagram must contain all        |                         |

| Procedure                      |             | domains necessary to describe the short-    |                         |

| Example - TLC<br>Example - SBC |             | comings.                                    |                         |

|                                |             | shortcomings must be stated using ele-      |                         |

| Phase 2                        |             | ments of the domain knowledge descrip-      |                         |

| Phase 3                        |             | tion.                                       |                         |

| Phase 4                        |             | the glossary contains the notions used      |                         |

| Phase 5                        |             | in D.                                       |                         |

| r hase 5                       |             | each entry in the list of possible develop- |                         |

|                                |             | ment alternatives must consider at least    |                         |

|                                |             | one of the shortcomings.                    |                         |

|                                |             |                                             |                         |

### Executing Phase 1 I

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary **Procedure** Example - TL<sup>i</sup> Example - SB<sup>i</sup>

Phase 2

Phase 3

Phase 4

Phase 5

All items of the output can be developed in parallel. The following points should be considered after we have an initial context diagram and some initial shortcomings:

- A shortcoming usually refers to some domains that must be introduced.

- Each domain requires a description of its domain knowledge.

- Each domain controls or observes some phenomena that must be decribed in the context diagram and may need a description in the glossary.

- For a shortcoming a new development alternative can be identified.

- A new development alternative may also address other shortcomings.

### Executing Phase 1 II

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL Example - SE

. . . . . . .

Phase 3

Phase 4

Phase 5

An assumption may show us that there are additional shortcomings.

### Remarks I

#### ES

Heisel

- Introduction

- DePES

- Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TII Example - S

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- Only the actual state is described.

- Possible solutions are discussed.

- Problem: Which domains should be described.

- Solution: Those domains, that are relevant for describing the shortcomings.

- For users in the environment a Hierarchical Task Analysis (HTA) can be performed, see

www.hfidtc.com/pdf/reports/HTA%20Literature%20Review.pdf .

- Other systems in the environment can be described by state machines (the notation is introduced in Phase 9).

- Do not forget to include the existing solution in the list of alternatives (even if it addresses no shortcoming).

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TL Example - SB

Phase 2

Phase 3

Phase 4

Phase 5

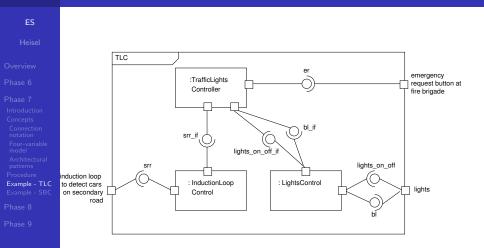

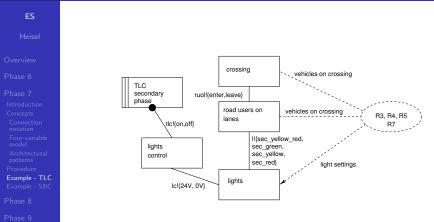

# **Example 1: traffic light control**

### Informal description of the task

E5

Heisel

Introductio

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC Phase 2

Phase 3

Phase 4

Phase 5

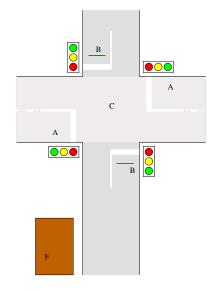

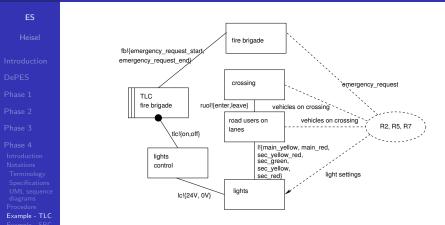

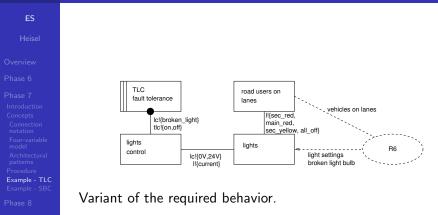

We should build a system that prevent accidents on the crossing. It should also help the fire brigade (on the left) to pass the crossing and arrange for a fair and adapted flow of traffic between the main road (horizontal) and the secondary road (vertical).

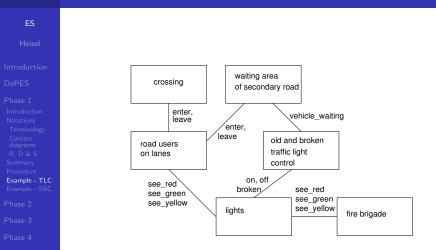

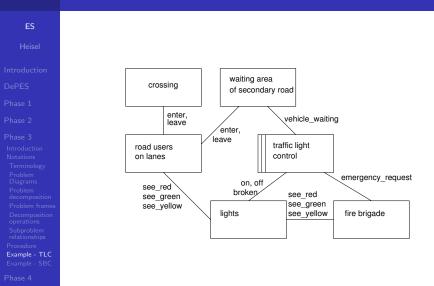

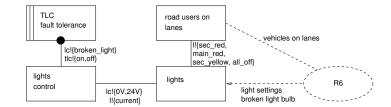

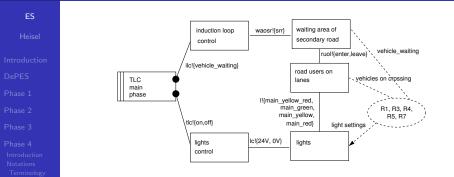

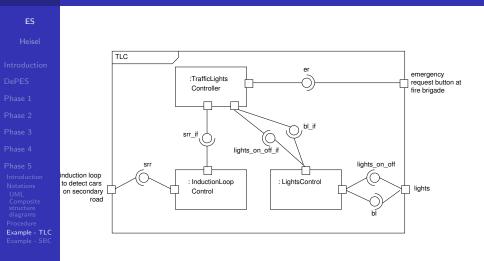

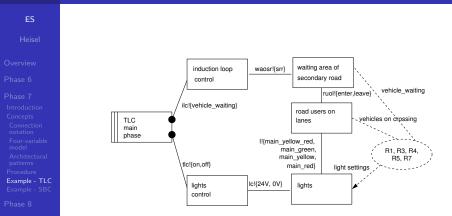

### Context diagram of system in use

Phase 5

### Shortcomings

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC

Phase 2

Phase 3

Phase 4

Phase 5

- SC1: The old traffic light control is broken and cannot be repaired and improved.

- SC2: Vehicles of the fire brigade are disturbed by cars on the secondary road when the secondary road is not allowed to pass. This causes delays in case of fire.

SC3: The amount of traffic has increased on both roads.

SC4: Too many accidents happened without working traffic lights.

### Domain knowledge: Facts I

ES

Heisel

Introduction

DePES

- Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure **Example - TLC** Example - SBC

- Phase 2

- Phase 3

- Phase 4

Phase 5

- F1 : Traffic rule: stop if red (see\_red).

- F2 : Traffic rule: cross if green. (see\_green)

- F3 : Traffic rule: leave crossing as fast as possible.

- F4 : Fair means (for this **crossing**) that vehicles on the main road are allowed to pass the crossing for more than twice the time vehicles of the secondary road are allowed.

- F5 : Traffic rule: if yellow (see\_yellow): stop if possible.

- F6 : Vehicles cannot stop immediately.

- F7 : A *broken* light bulb can be detected by measurement of the electric current (no current = no light).

- F8 : There are tunnels for pedestrians.

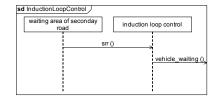

- F9 : Induction loops can be used for monitoring the **waiting** area of secondary road.

### Domain knowledge: Facts II

#### ES

Heisel

- Introduction

- DePES

- Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- F10: The **lights** operate with a power supply of 24 V.

- F11: The **fire brigade** is allowed to ignore the red light (but must be careful).

- F12 : If the red phase is more than 30 s, some car drivers ignore the red light.

- F13 : The **old traffic light control** is broken and cannot be repaired. Before, the vehicles on the main road were allowed to pass until a vehicle on the secondary road was detected. Cars in the secondary road were allowed to pass for 5 seconds.

### Domain knowledge: Assumptions

Phase 2

Phase 3

Phase 4

- A1 : All vehicles follow the traffic rules.

- A2 : Pedestrians use the pedestrian tunnels.

# Glossary for crossing

- Iane / waiting area of main road: A lane / waiting area of secondary road: B traffic lights: device containing colored light bulbs to signal "stop" or "go" fire brigade: F

- crossing: critical section: C

- vehicle waiting: sensor detecting if a vehicle is in the waiting area of the secondary road

- accident: 2 or more vehicles at the same time at the same place

### List of development alternatives

#### ES

Heisel

#### Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC

- Phase 3

- Phase 4

- Phase 5

- ALT1: Remove old traffic lights and use signs (addresses shortcoming SC1)

- ALT2: Replace old traffic lights by a roundabout/rotary (addresses shortcomings SC1, SC3, and SC4)

- ALT3: Replace the broken traffic lights control by a new traffic lights control (addresses shortcomings SC1, SC2, SC3 and SC4)

- ALT4: Leave everything as it is

### Validation I

#### ES

Heisel

Introductio

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC Phase 2

Phase 3

Phase 4

Phase 5

All domains domains and phenomena in the context diagram are described:

crossing: F4 road users on lanes: F1, F2, F3, F5, F6, F12, A1 waiting area of secondary road: F9 old and broken traffic light control: F13 lights: F10, F7 fire brigade: F11

The pedestrians are not considered in the context diagram, since pedestrian tunnels exists and are used (F8, A2). The

# Validation II

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC

Phase 2

Phase 3

Phase 4

Phase 5

context diagram contains all domains necessary to describe the shortcomings and the shortcomings are stated using elements of the domain knowledge description.

- SC1: old and broken traffic light control

- SC2: fire brigade, waiting area of secondary road, road users on lanes

- SC3: old and broken traffic light control

- SC4: old and broken traffic light control

The glossary shoud contain the notions used in D. The given TLC glossary is just an example and not complete. Each entry in the list of possible solutions considers at least one of the shortcomings. This is directly stated on the corresponding slide.

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC

Phase 2

Phase 3

Phase 4

Phase 5

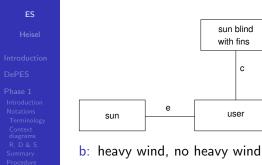

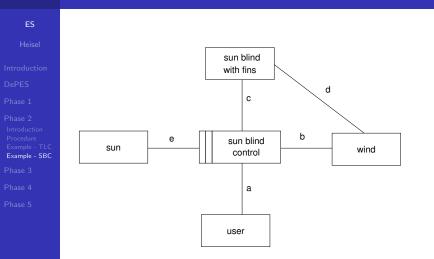

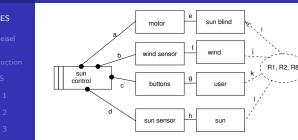

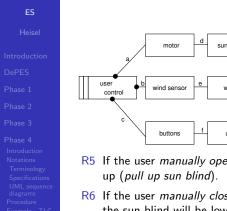

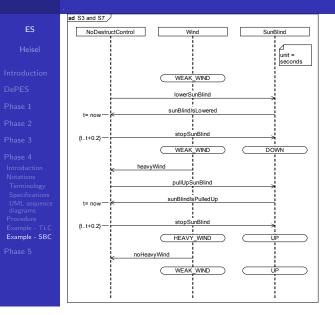

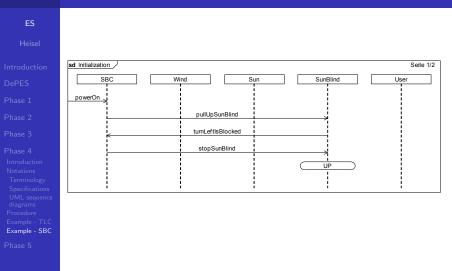

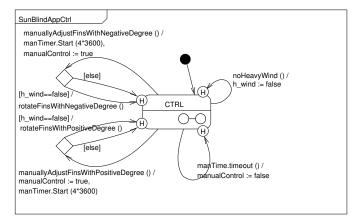

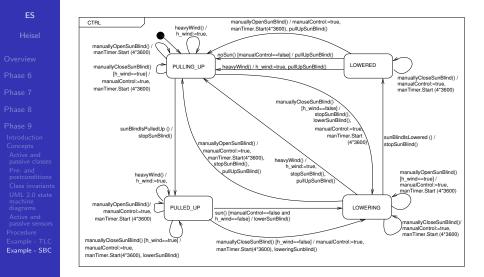

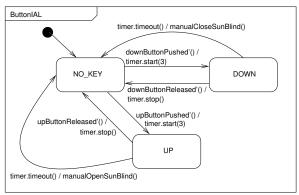

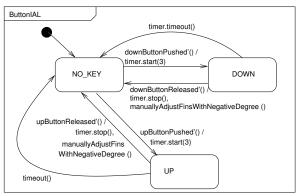

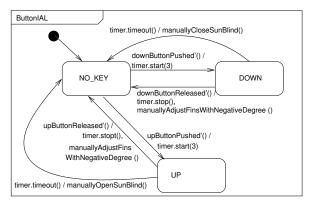

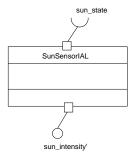

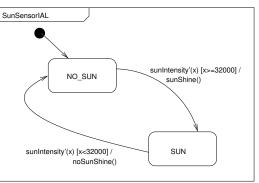

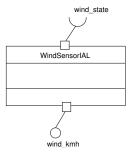

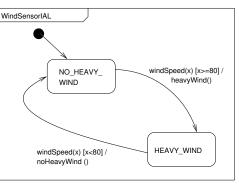

# Example 2: sun blind control

#### Informal description of the task

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC

Phase 3

Phase 4

Phase 5

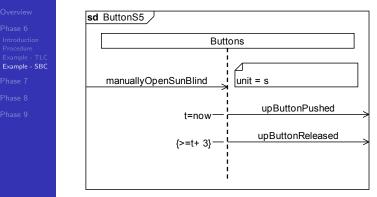

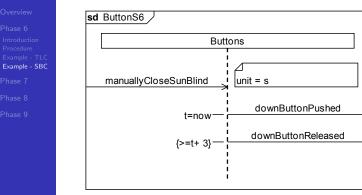

A building is equipped with sun blinds made up of metallic fins which are attached to the outer side of the window. The sun blinds are controlled manually. Unfortunately, the sunblinds can be destroyed by heavy wind if they are not pulled up. The system should be improved to achieve a comfortable working ambiance by not disturbing the users by sunshine.

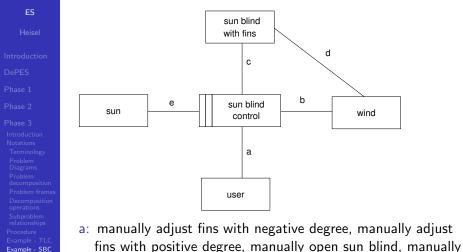

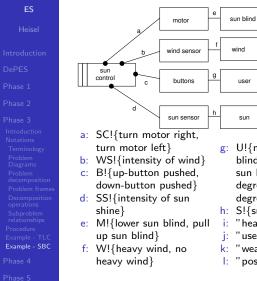

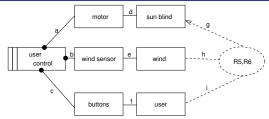

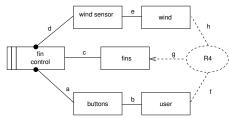

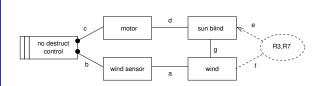

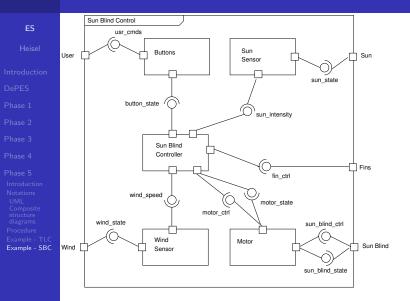

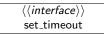

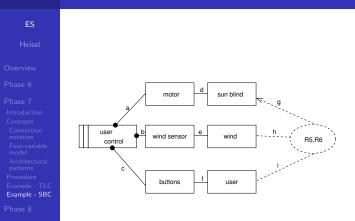

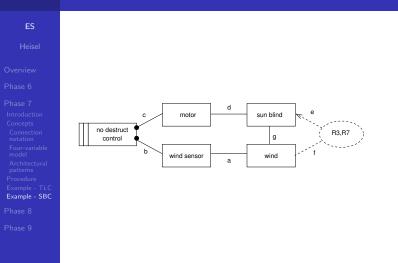

### Context diagram of system in use

Example - SBC

c: lower sun blind, pull up sun blind, stop sun blind, sun blind is lowered, sun blind is pulled up, rotate fins with positive degree, rotate fins with negative degree

С

user

d

wind

b

- d: destroy sun blind

- e: sunshine. no sunshine

### Shortcomings

#### ES

#### Heisel

- Introduction

- DePES

- Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC

- Phase 2

- Phase 3

- Phase 4

- Phase 5

- SC1: Users forget to pull up the sunblind when there is no sunshine what may have an influence on the well-being and health of users.

- SC2: Users forget to pull up the sunblind when there is heavy wind or even do no recognize that there is heavy wind.

- SC3: Users have to stop their work to lower the sunblind if there is sunshine with high intensity and the users cannot read their monitor content.

- SC4: Sometimes users destroy the sunblind accidentally by pulling heavily at the wires.

#### Facts

#### ES

Heisel

- Introduction

- DePES

- Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC

- Phase 2

- Phase 3

- Phase 4

- F1: Interface between user and sun blind are the control wires.

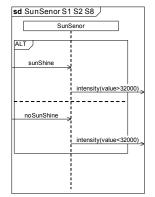

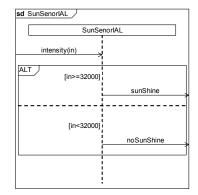

- F2: The intensity of sunshine on a sunny day ranges from 32 000 lux to 100 000 lux. More than 32 000 lux makes it hard to read content of a standard monitor.

- F3: The fins are turnable from  $80^{\circ}$  to  $0^{\circ}$  and to  $-80^{\circ}$ . If a user tries to rotate more (with normal power), nothing happens.

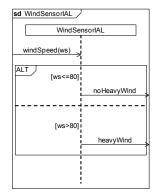

- F4: Heavy wind has a speed of more than 80 kilometers per hour. No heavy wind has a speed of less than 80 kilometer per hour.

- F5: The sun blind is destroyed by heavy wind.

- F6: The sun blind is destroyed if the user pulls too heavily at the wires (especially if the sunblind is lowered or pulled up).

- F7: The fins have an interface that can be directly connected to a microcontroller.

#### Assumptions

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC

Phase 2

Phase 3

Phase 4

Phase 5

Assumptions, description of user:

- A1: Users usually lower the sunblind when the sun is shining.

- A2: Users pull up the sunblind when the sun is not directly shining

- A3: Users pull up the sunblind when there is heavy wind.

- A4: Users adjust the fins as convenient.

- A5: User recognize if the wind is blowing heavily (heavy wind).

- A6: Users pull up the sunblind when they want to look out of the window.

- A7: Users lower the Sunblind when they do not want to be seen.

# Glossary for sun blind (example)

ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC Phase 2 Phase 3

Phase 4

Phase 5

metallic fins: metallic plates rotating on a horizontal axis.

outer side: not inside the building.

windows: part of a building made of glass.

sun blind: is made up of *metallic fins* which are attached to the *outer side* of the *window*.

sinshine: ...

Designations:

wind: ... wire: ...

microcontroller: ...

monitor: ...

### List of development alternatives

ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC

Phase 2

Phase 3

Phase 4

- ALT1: Hire an employee who pulls up all sunblinds in case of heavy wind. (addresses shortcoming SC1)

- ALT2: Replace sunblinds by drapes or other types of sunblinds. (addresses shortcomings SC2 and SC4)

- ALT3: Replace the display units by monitors with higher intensity and let the sunblind pulled up. (addresses shortcomings SC1, SC2, SC3, and SC4)

- ALT4: Automatic sunblind control (addresses shortcomings SC1, SC2, SC3, and SC4)

- ALT5: Leave everything as it is

### Validation I

#### ES

Heisel

#### Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC Phase 2

Phase 3

Phase 4

Phase 5

All domains domains and phenomena in the context diagram are described:

```

User: A1 - A7, F1

Wind: F4, F5

Sunblind with fins: F1, F3, F5, F6, F7

Sun: F2

```

# Validation II

#### ES

Heisel

Introduction

DePES

Phase 1 Introduction Notations Terminology Context diagrams R, D & S Summary Procedure Example - TLC Example - SBC

Phase 2

Phase 3

Phase 4

Phase 5

The context diagram contains all domains necessary to describe the shortcomings and the shortcomings are stated using elements of the domain knowledge description.

- SC1: User, Sun, and Sunblind

- SC2: User, Wind, and Sunblind

- SC3: User, Sunblind (monitor intentionally left out, seen as part of user domain)

- SC4: User, Sunblind (wires intentionally left out, seen as part of Sunblind domain)

The glossary contains exactly the notions used in D, but is not complete. Each entry in the list of possible solutions considers at least one of the shortcomings. This is directly stated on the corresponding slide.

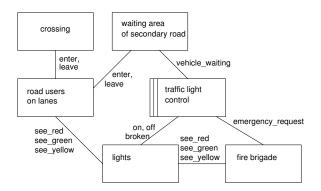

### Phase 2: Describe system to be built

ES

Heisel

Introduction

DePES

Phase 1

Phase 2 Introduction Procedure Example - TLC Example - SBC

Phase 3

Phase 4

Phase 5

- 1. Describe system in use

- 2. Describe system to be built

- 3. Decompose problem

. . .

- 4. Derive machine behavior specification for each subproblem

- 5. Design global system architecture

- 6. Derive specifications for all components of the global system architecture

- 7. Design a software architecture for all components of the global system architecture that should be implemented in software

- 8. Specify the behavior of all components of all software architectures, using sequence diagrams

#### Phase 2: Describe system to be built

| ES                      | input:      | all results of Phase 1                        | Jackson/ natural lan-   |

|-------------------------|-------------|-----------------------------------------------|-------------------------|

| 23                      |             |                                               | guage                   |

| Heisel                  | output:     | system mission statement                      | natural language        |

|                         |             | selected development alternatives             | natural language        |

| Introduction            |             | context diagram of system to be built         | ext. Jackson            |

| DePES                   |             | changed domain knowledge $D(F \land A)$       | natural language, (HTA, |

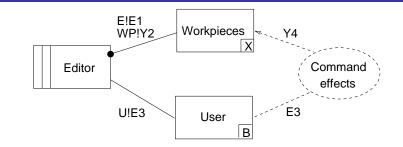

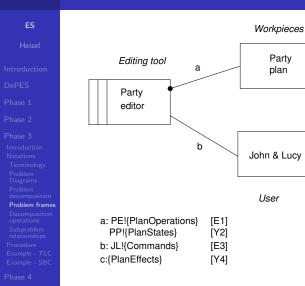

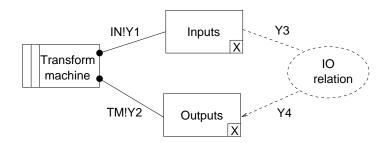

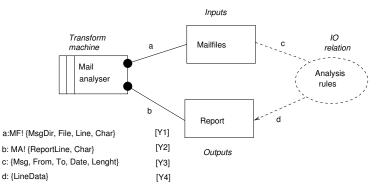

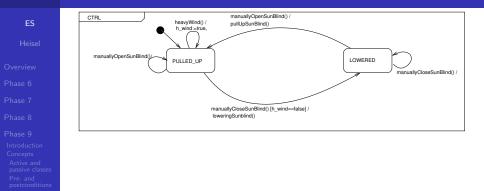

| Phase 1                 |             |                                               | state machines)         |